Part 2. Discussion

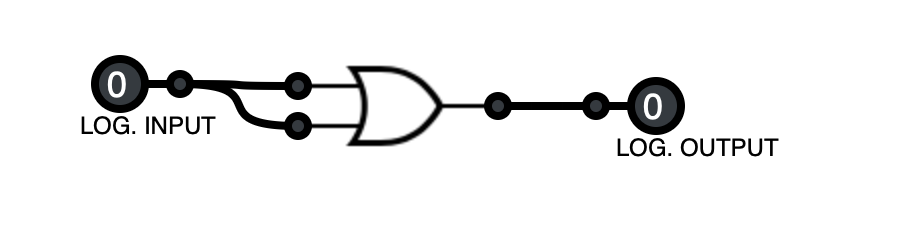

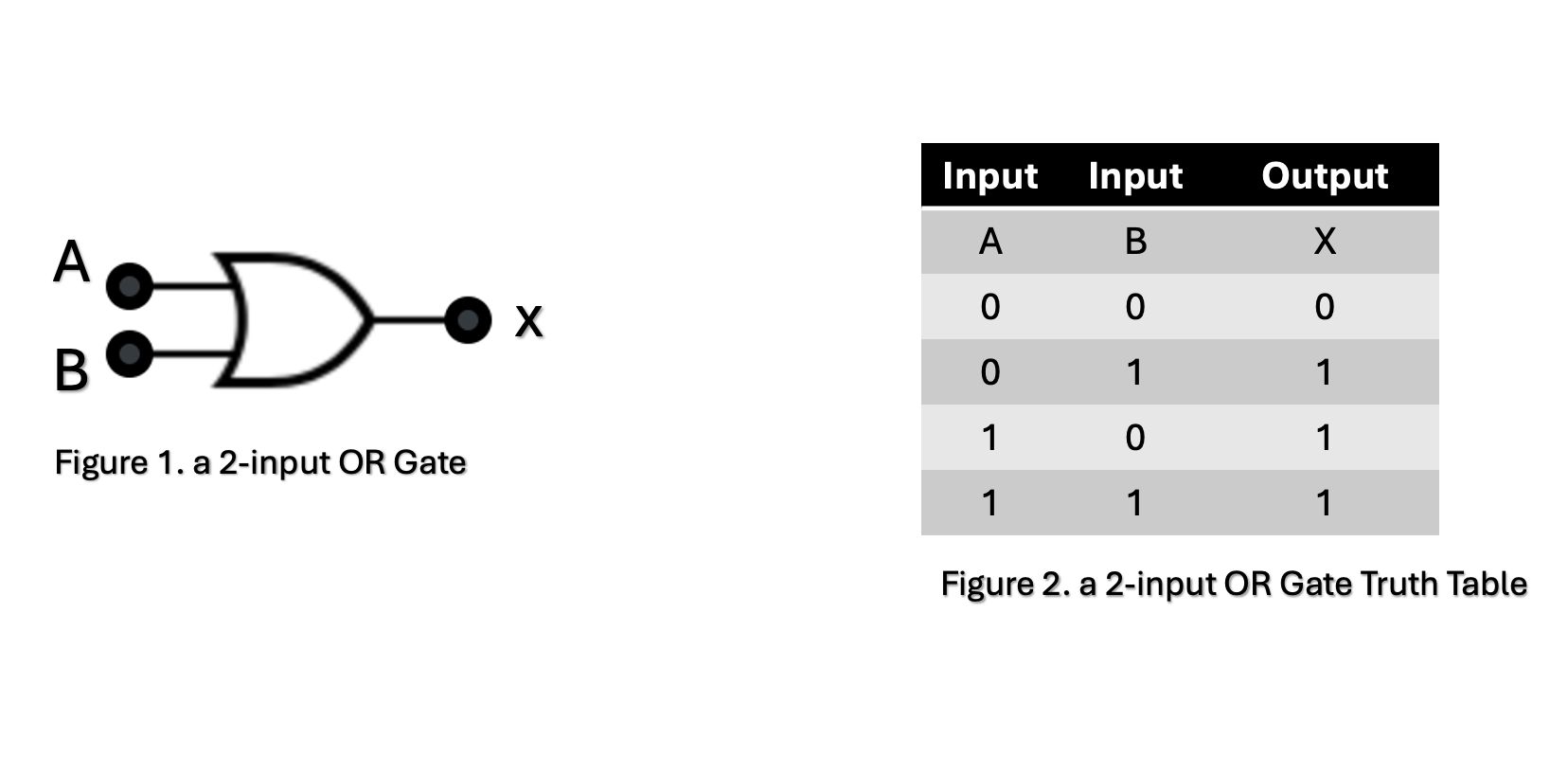

An OR gate is designed so that an output signal will occur any time there is an input signal. The presence of a signal is represented as logic 1 and the absence of a signal is represented as logic 0. A symbol for a two-input OR gate is shown in figure 1-1a.

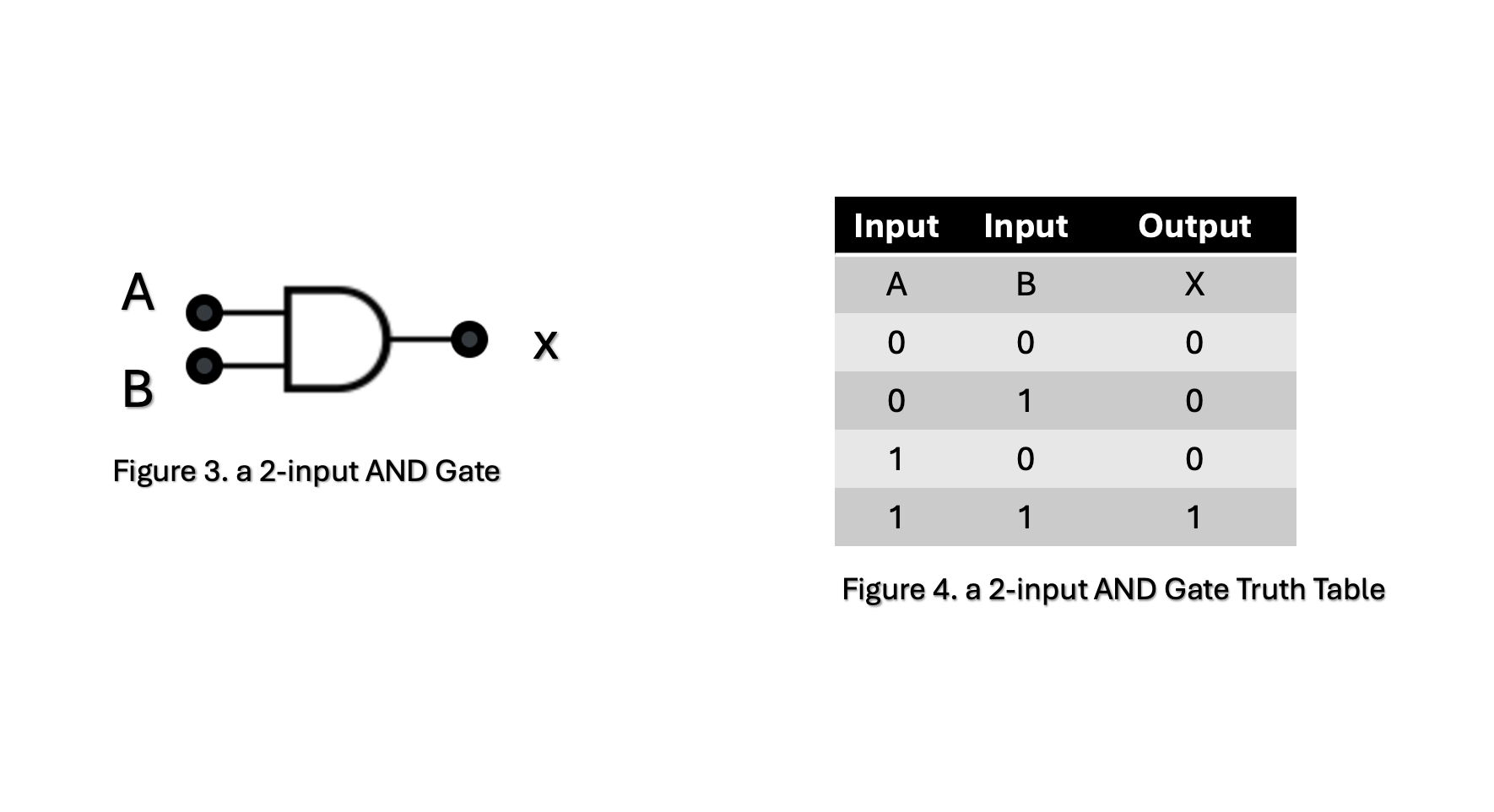

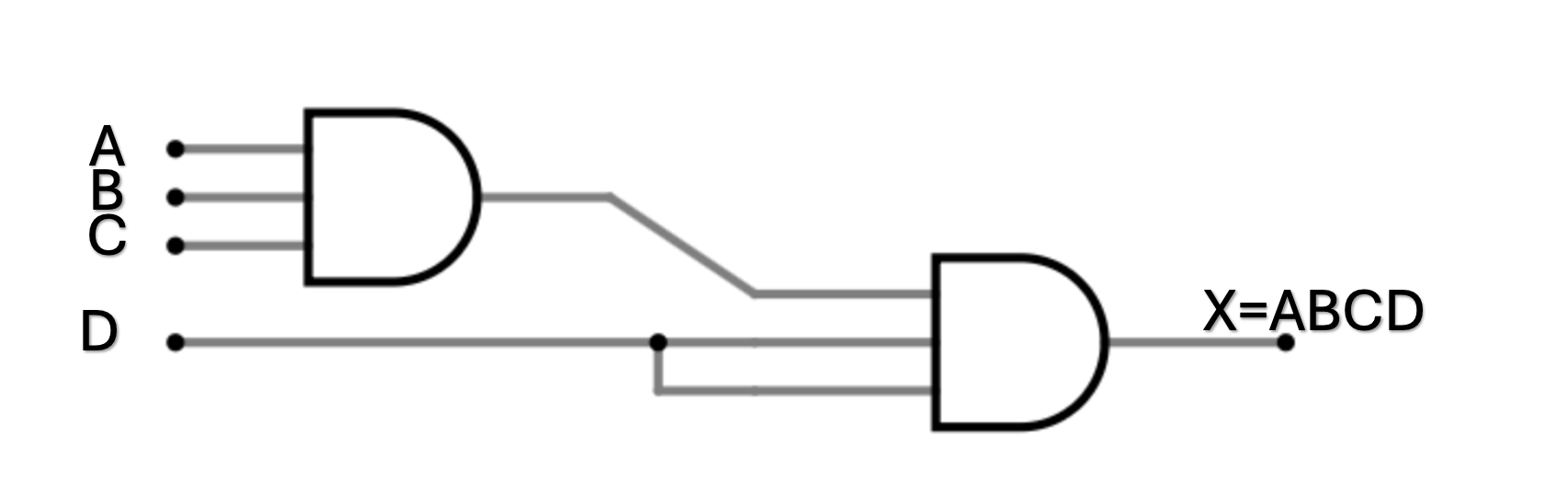

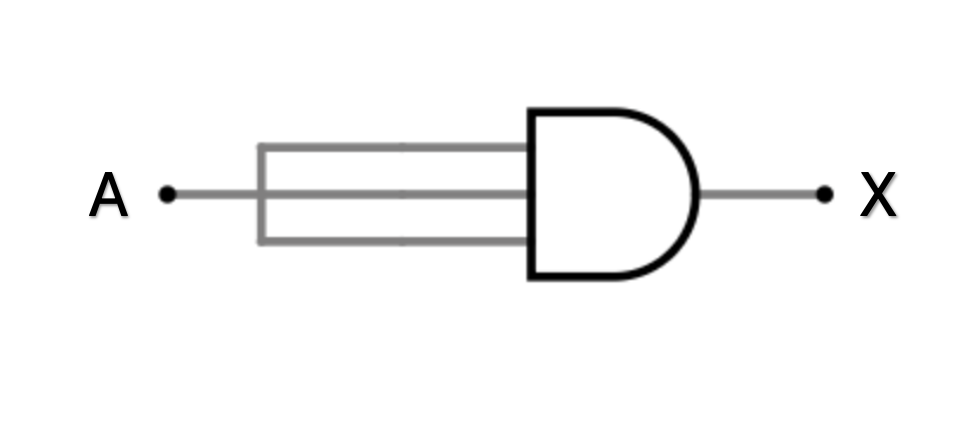

An **AND gate** is designed so that an output signal will occur only when there are signals at all inputs.